Philip J. McNally, Thane Smith, Fred R. Phelleps, and Kathleen M. Hogan

COMSAT Laboratories, 22300 COMSAT Drive, Clarksburg, MD 20871

Bryce Smith

Hughes Aircraft, Space and Communications Group,

1950 East Imperial Highway, El Segundo, CA

Harry Deitrich

Naval Research Laboratory, Washington DC

### Abstract

An all ion-implant, planar process has been used to fabricate high-Q, hyper-abrupt carrier profile, varactor diodes as components of GaAs MMIC VCOs with state-of-the-art performance. These GaAs varactor-tuned FET oscillators operate up to 24 GHz with a tuning bandwidth of 5 GHz in K-band. The high-Q varactors feature a buried N<sup>+</sup> layer created by ion-implantation at up to 6 MEV. Separately masked implanted N<sup>+</sup> areas connect the buried layer to ohmic contacts at the surface. Varactor f<sub>c</sub> of 1600 GHz was obtained at 0.09 pF.

### INTRODUCTION

Varactor diodes have wide application in microwave circuits, including local oscillators (1)-(7), efficient frequency multipliers (8),(9), and phase-shift elements (10),(11). Potential system applications include receivers, frequency converters, and phased array antennas. However, the use of varactors in GaAs MMICs has been limited by low quality factor (Q). High Q requires a low resistance conduction path from the depletion layer edge to the ohmic contact of the diode. A relatively thick low resistance N<sup>+</sup> back-contact layer under the active layer of the varactor is needed for high Q. Most MMIC processes used to obtain such an N<sup>+</sup> layer are not compatible with the fabrication of FETs, because FETs require semi-insulating material under the active layer. Processes using epitaxial layers are possible, but they require a two-level (at least) mesa etch process that results in a very non-planar surface and a reduction in yield. Previous FET-based VCOs (varactor controlled oscillators) omitted the N<sup>+</sup> back contact, compromising Q. The best reported results (1) for this type of VCO show a maximum Q of 3.3 at 15 GHz; thus, the cut-off frequency, f<sub>c</sub>, (product of frequency times Q) is 50 GHz. One way around the problem is to use IMPATT diodes instead of FETs in a VCO (3)-(5), but GaAs IMPATT diodes have excessive high phase noise, which is detrimental to system performance.

A new, monolithic, high-Q, Schottky-barrier varactor process, compatible with FETs, has been developed by COMSAT (12). It uses ion implantations up to 6 MEV to create buried N<sup>+</sup> areas for low-resistance back contacts. This work has drawn heavily on previous studies carried out at NRL (13). Lower energy implants are used to create the other conducting layers required in the MMIC. The process is all ion-implant and

planar, and therefore capable of providing high yield. This process has been used by us to fabricate K<sub>u</sub>- and K-band FET based VCOs along with discrete FETs and varactors on the same wafer.

### VARACTOR DESIGN

The variation of varactor capacity with voltage is often characterized by a parameter, gamma. The capacity, C, is given by the following formula.

$$C = \frac{A}{(V + V_0)^\gamma}$$

Where A and V<sub>0</sub> are constants. The varactors were designed to have hyper-abrupt carrier profiles for a  $\gamma$ -value of 1.2. A  $\gamma$  of 2.0 would provide linear variation of frequency with tuning voltage. Instead, the 1.2 value was chosen because computer modeling showed that this reduces the series resistance while providing an acceptable F vs V<sub>t</sub> curve. The required carrier profile shape has carrier density vs depth, x, varying as x<sup>a</sup>, for  $\gamma = 1.2$ ,  $a = -1.167$ . With the help of a computer program, this shape was approximated by several silicon implantations modeled as Gaussian distributions (14).

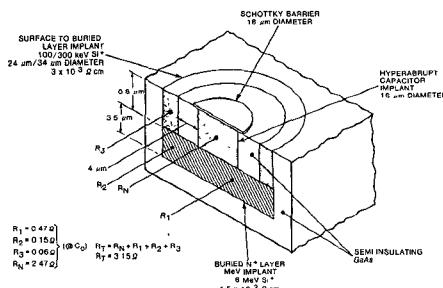

The varactor diode contains the three implanted regions shown in Figure 1. Only the upper portion of the hyper-abrupt profile is implanted in the cylinder below the Schottky barrier. The lower portion is included with the buried layer. This strategy reduces series resistance at low bias values by decreasing the depth at which the current begins to flow parallel to the GaAs surface. Surface contact to the buried layer is provided by multiple low energy N<sup>+</sup> ion implants. Ohmic contacts are formed on this region. The resulting diode structure is planar. Between the GaAs surface and the top of the buried layer, a high resistivity annular ring separates the N<sup>+</sup> and hyper-abrupt regions. It provides electrical isolation and serves as a guard ring for achieving low-leakage high breakdown voltage at the Schottky barrier. The diameter of the Schottky junction is adjusted to provide the various zero-bias capacity values required in the MMIC VCO.

### MMIC VCO DESIGN

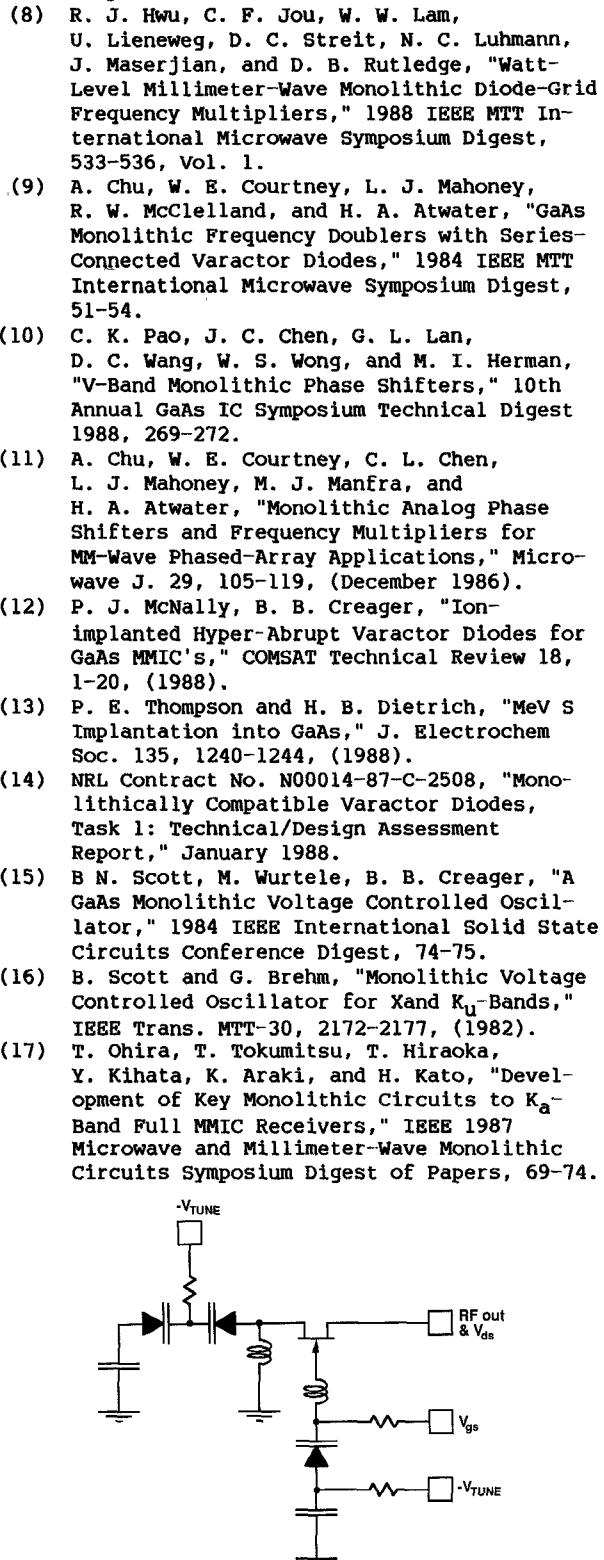

A common gate FET oscillator circuit topology, Figure 2, was chosen to evaluate the performance of the planar varactor process. This type

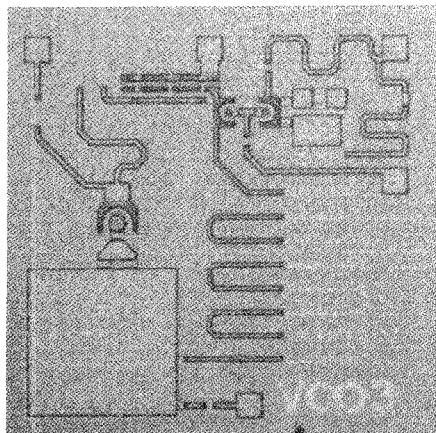

of circuit has been shown to be successful for monolithic varactor tuned FET oscillators through K<sub>u</sub>-Band (1), (15)-(16). The circuit design was developed using discrete components fabricated by the same process. The chips were characterized and then assembled using short wire-bond interconnects between the GaAs chips, yielding a pseudo-monolithic circuit. This provided sufficient information for the MMIC designs. Several circuit layouts using different combinations of varactors were included to cover different frequency bands. A photograph of one of the MMIC VCO chips is shown in Figure 3. Each design incorporates a 0.5- $\mu$ m by 150- $\mu$ m GaAs MESFET, 2 to 4 tuning varactors, thin film capacitors, GaAs resistors, microstrip meander lines, and via-hole grounding.

#### FABRICATION

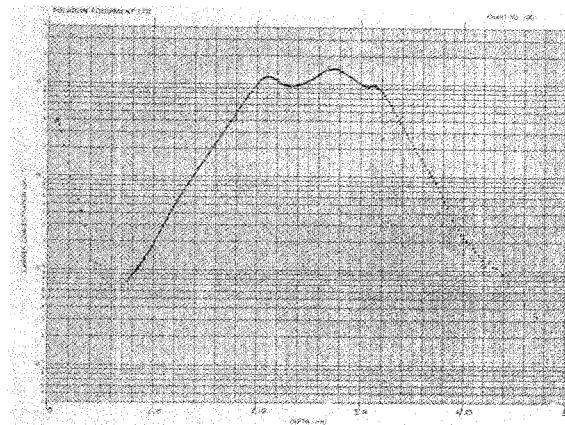

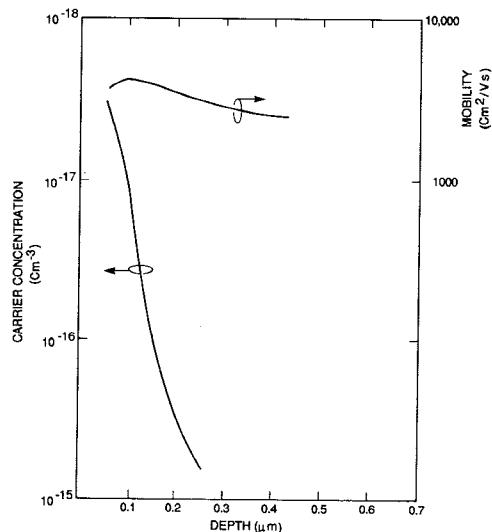

The N<sup>+</sup> anode (back contact) region in the buried layer is created by co-implanting Si<sup>+</sup> and S<sup>+</sup> at 6 Mev energy, using a three micron thick plated-gold mask. The same mask was used for the lower energy implants to produce the deep portion of the hyper-abrupt profile. All implantations at energies above 300 keV were performed by Universal Energy Systems, Inc. of Dayton, Ohio. The lower energy implants are masked using AZ 1375J photoresist. These include the upper portion of the hyper-abrupt profile, the FET active layer, and the N<sup>+</sup> connection between the buried layer and the ohmic contact locations. The resulting carrier profile in the GaAs below the Schottky barrier location is shown in Figure 4. The buried layer has measured sheet resistance of 9 to 12 ohms per square. Surface contact to the buried layer is provided by N<sup>+</sup> implants at several energies up to 300 keV. Ohmic contacts are formed on this N<sup>+</sup> region. The carrier profile of the FET active layer is shown in Figure 5. A single post implant activation step is performed using a silicon nitride cap and rapid thermal anneal at 980°C for 10 s. Process monitoring of the implantation was performed using separate monitor wafers. Carrier profiling and sheet resistance measurements were made on the monitor wafers.

After implant activation, the photo-resist lift-off mask for varactor Schottky contacts and capacitor bottom plates is used to mask a 750 Å recess etch. The Ti/Pt/Au metal is then deposited by e-beam evaporation. COMSAT's standard process steps are used for FET gates, air-bridges and electro-plated gold conductors. The 0.5- $\mu$ m FET gates and portions of the meander lines were defined by e-beam lithography. Other lithographic steps were performed using conventional photolithography.

After front side completion, the wafers are subjected to DC characterization using an array of process monitor patterns and an automatic probing system. Uniformity and reproducibility of 5 percent is obtained. Following these tests, the wafers are thinned to 100  $\mu$ m, via-holes are etched from the back, and the back side is metalized and electroplated. Dicing is performed face up using a dicing-saw.

#### MEASUREMENTS

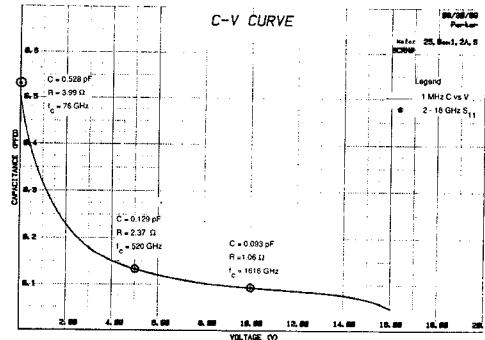

Discrete varactors, fabricated on the same wafer as the MMIC VCOs, were characterized from 2 to 18 GHz to determine the variation of their one-port S-parameters. For this purpose they were mounted in a test fixture at the end of a 50- $\Omega$  microstrip line. The varactor cathode was wire bonded to the top conductor of the line. The anode of the varactor and the microstrip line ground plane were both grounded. S-parameter data were fitted to a series RLC equivalent circuit. Excellent fits were obtained. The inductance values were consistent with the wire bond lengths. R and C values found in this way were used to calculate the varactor cutoff frequency, f<sub>c</sub>, which determines the quality factor Q for any given frequency. Figure 6 compares the data obtained from the S-parameter measurements at 0, 5, and 10 V across the varactor to the 1-MHz C vs V data for the same diode. The agreement of capacity values is excellent. For a capacity of 0.50 pF, which occurs near zero bias voltage, f<sub>c</sub> of this varactor is 100 GHz. This rises to 1600 GHz at -10 V.

Discrete 0.5- $\mu$ m x 150- $\mu$ m FETs, fabricated on the same wafer as the MMIC VCOs, were characterized for their 2-port S-parameters from 2 to 18 GHz. A maximum frequency of oscillation of 63.4 GHz was calculated from these data.

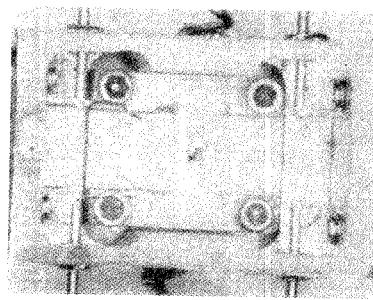

The MMIC VCO chips were mounted on Kovar carriers using 0.010-in. thick alumina substrates with tantalum nitride static protection resistors. DC and RF connections to the MMIC chip are via these substrates. A photograph of the test fixture with a VCO3 die is shown in Figure 7. The gate and drain bias were adjusted separately to optimize tuning bandwidth and RF power output. A small amount of tuning on the RF output line helped to improve the matching of the VCO chip to it.

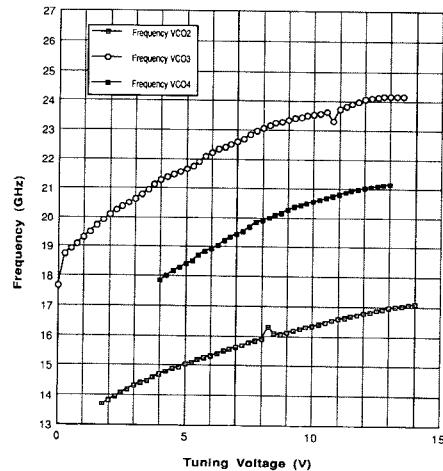

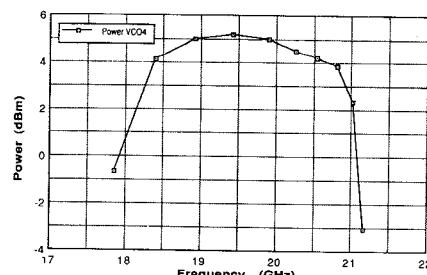

As shown in Figure 8, tuning bandwidth of over 5 GHz was obtained with up to +5 dBm output power (Figure 9). These data are comparable to those of Rease and Beall (1), but our Q values are higher. This allows a higher maximum frequency to be reached.

#### CONCLUSION

Commercially available high energy implantation services have been used to develop a planar ion implant process for the fabrication of high-Q monolithically compatible varactors in semi-insulating GaAs wafers. This process was used to fabricate several different MMIC VCOs and discrete varactors. These have exhibited state-of-the-art performance. A tuning bandwidth of over 5 GHz and output power of +5 dBm were obtained from K-band MMIC VCOs. 0.5-pF discrete varactors show a cut-off frequency (product of f times Q) of 100 GHz, which increases to 1600 GHz when the capacity is decreased to 0.09 pF at a bias voltage of -10 V.

High-Q varactors are useful in many microwave applications. We believe that this high-yield process makes it practical to include them in MMICs.

## ACKNOWLEDGMENTS

This work has been supported, in part, by the Naval Research Laboratory under Contract No. N00014-87-2508, and by Hughes Aircraft Corp., Space and Communications Group IR&D, under Purchase Order No. 08-996546-LCR. Additional R&D funding has been provided by Dr. John V. Evans, Director of COMSAT Laboratories. The authors extend special thanks to Phil Thompson of NRL for in-depth technical discussions of the application of MeV ion implantation to monolithically compatible varactor diodes, to Bryan Adams and Rex Olson of Hughes Aircraft Co. for assembly and test of the MMIC VCO chips, to COMSAT Laboratories' MMIC Evaluation and Assembly Department for their skillful assembly of varactors and FETs for RF measurement, to Tim Lee and John Upshur for S-parameter measurements on varactors and FETs, to Gene Carlson and Dick Porter for skillful DC and 1-MHz characterization, and to the Microelectronics Pilot Line Department for their meticulous attention to every detail of the MMIC fabrication.

## REFERENCES

- (1) E. Reese and J. M. Beall, "Optimized X- and K<sub>u</sub>-Band GaAs MMIC Varactor-Tuned FET Oscillators," 1988 IEEE MTT International Microwave Symposium Digest, 487-490, Vol. 1.

- (2) G. E. Brehm, B. N. Scott, and F. H. Doerbeck, "Fabrication Techniques for X-Band Monolithic VCO's," 1982 IEEE MTT International Microwave Symposium Digest, 57-60.

- (3) N.-L. Wang, W. Stacey, R. C. Brooks, K. Donegan, and W. E. Hoke, "Millimeter-Wave Monolithic GaAs IMPATT VCO," IEEE Trans. MTT-36, 1942-1947, (1988).

- (4) B. Bayraktaroglu, "Monolithic 60-GHz GaAs IMPATT Oscillators," IEEE Trans. MTT-36, 1925-1929, (1988).

- (5) B. Bayraktaroglu, "Monolithic 60-GHz GaAs CW IMPATT Oscillator," 1988 IEEE MTT International Microwave Symposium Digest, 63-66, Vol. 1.

- (6) G. Pataut and D. Pavlidis, "X-Band Varactor-Tuned Monolithic GaAs FET Oscillators," International J. Electronics 64, 731-751, (1988).

- (7) T. Ohara, T. Tanaka, and H. Kato, "A 14-GHz band Monolithic Voltage Controlled

- (8) R. J. Hwu, C. F. Jou, W. W. Lam, U. Lieneweg, D. C. Streit, N. C. Luhmann, J. Maserjian, and D. B. Rutledge, "Watt-Level Millimeter-Wave Monolithic Diode-Grid Frequency Multipliers," 1988 IEEE MTT International Microwave Symposium Digest, 533-536, Vol. 1.

- (9) A. Chu, W. E. Courtney, L. J. Mahoney, R. W. McClelland, and H. A. Atwater, "GaAs Monolithic Frequency Doublers with Series-Connected Varactor Diodes," 1984 IEEE MTT International Microwave Symposium Digest, 51-54.

- (10) C. K. Pao, J. C. Chen, G. L. Lan, D. C. Wang, W. S. Wong, and M. I. Herman, "V-Band Monolithic Phase Shifters," 10th Annual GaAs IC Symposium Technical Digest 1988, 269-272.

- (11) A. Chu, W. E. Courtney, C. L. Chen, L. J. Mahoney, M. J. Manfra, and H. A. Atwater, "Monolithic Analog Phase Shifters and Frequency Multipliers for MM-Wave Phased-Array Applications," Microwave J. 29, 105-119, (December 1986).

- (12) P. J. McNally, B. B. Creager, "Ion-implanted Hyper-Abrupt Varactor Diodes for GaAs MMIC's," COMSAT Technical Review 18, 1-20, (1988).

- (13) P. E. Thompson and H. B. Dietrich, "MeV S Implantation into GaAs," J. Electrochem Soc. 135, 1240-1244, (1988).

- (14) NRL Contract No. N00014-87-C-2508, "Monolithically Compatible Varactor Diodes, Task 1: Technical/Design Assessment Report," January 1988.

- (15) B. N. Scott, M. Wurtele, B. B. Creager, "A GaAs Monolithic Voltage Controlled Oscillator," 1984 IEEE International Solid State Circuits Conference Digest, 74-75.

- (16) B. Scott and G. Brehm, "Monolithic Voltage Controlled Oscillator for X and K<sub>u</sub>-Bands," IEEE Trans. MTT-30, 2172-2177, (1982).

- (17) T. Ohira, T. Tokumitsu, T. Hiraoka, Y. Kihata, K. Araki, and H. Kato, "Development of Key Monolithic Circuits to K<sub>a</sub>-Band Full MMIC Receivers," IEEE 1987 Microwave and Millimeter-Wave Monolithic Circuits Symposium Digest of Papers, 69-74.

Figure 1. Cross-Section of the Planar Ion-Implanted Hyperabrupt Varactor Diode

Oscillator-Application to a Microwave Phase-Locked Loop," Trans. Inst. Electronics and Communication Labs., Part C (Japan), J68C, 1156-1158, (1985).

Figure 2. Typical VCO Schematic

Figure 3. Photograph of a Typical  $0.75\text{-}\mu\text{m}$  Square MMIC VCO Chip

Figure 4. Ion Implanted Carrier Profile for Varactor Diodes Showing Both Shallow and Buried Portions Before the  $750\text{ \AA}$  Recess Etch

Figure 5. Ion Implanted Carrier Profile for the FET Active Layer

Figure 6. 2-18 GHz Varactor Characterization Data Compared to the 1-MHz  $V$  vs  $V$  data

Figure 7. MMIC VCO3 Mounted in the Test Fixture Described in the Text

Figure 8. Frequency vs Tuning Voltage for Three Different MMIC VCO Chips

Figure 9. Output Power vs Frequency Curve for the VCO4 Chip